量价齐升,设备行业躺赢

摩尔定律是指随着技术演进,芯片上容纳的晶体管数量会呈指数级增长,每1.5-2年翻一倍,同时带来芯片性能提升一倍或成本下降一半的效应。半导体制造中,工艺制程持续微缩导致晶体管密度逼近极限,同时存在短道沟效应导致的漏电、发热和功耗严重问题。

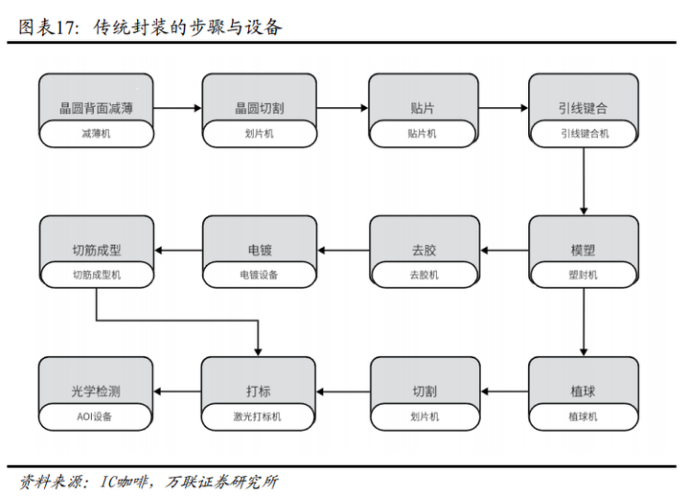

后摩尔时代,先进封装成为趋势。先进封装是在不要求提升芯片制程的情况下,实现芯片的高密度集成、体积的微型化,并降低成本,符合高端芯片向尺寸更小、性能更高、功耗更低演进的趋势。传统封装的功能主要在于芯片保护、电气连接,先进封装在此基础上增加了提升功能密度、缩短互联长度、进行系统重构的三项新功能。在后摩尔时代,人们开始由先前的“如何把芯片变得更小”转变为“如何把芯片封得更小”,先进封装成为半导体行业发展重点。

据Yole数据,2026年先进封装全球市场规模475亿美元,2020-2026E CAGR约7.7%。未来,随着算力需求增加催化Cowos提速渗透,叠加国内安全自主可控需求,将加速推动我国封测、设备、材料等相关产业链环节革新与国产化进程。

国内封测龙头公司主要是通富微电、长电科技、晶方科技、甬矽电子、伟测科技等。今天我们主要从封装工艺的角度看上游设备行业的投资机会。

一、当下先进封装设备行业的两个基本逻辑:

1、传统半导体设备的技术可控。

根据行业专家反馈,目前招投标会考虑完全国产化的设备。这将从而带动封装设备的国产化的进程。

从国产替代的角度来看,封装设备在整个半导体设备的产业链中属于门槛和难度较低的环节。但封装设备的国产化率不高,核心原因是过去封测厂主要给海外的龙头企业去做代工为主,设备选型上的自主性不大。竞争格局上,主要是海外的龙头对整个设备的垄断。

2、传统封装设备的技术迭代进化。

先进封装是后摩尔时代的一个大的发展趋势。当前,随着AI产业的发展,芯片性能的提升、国产芯片产业在受控中发展突破,先进封装产业正在迎来新的发展机遇。

国内先进封装的渗透率大幅度低于全球,有比较大的发展空间,并且随着整个半导体技术节点的进步,或为了绕开国外的一些卡脖子限制,多重因素影响下,国内先进封装渗透率将加速提升。

先进封装的一个核心点是倒装工艺对传统引线间隔工艺的替代。

倒装工艺对传统工艺替代中包括LDI或用光刻、回流焊、塑封等环节和PCB的工艺环节相吻合。这就给PCB相关设备带来了一个发展的新机遇。

从产业发展来看,部分龙头公司已经开始拓展先进封装设备研发,进度快的可能已经送客户验证或者有一些已经拿到了客户的订单。

对于这些公司而言,过去市场是按PCB的设备公司来进行定价的,后续随着先进封装设备的突破,可能有望迎来估值的切换。先进封装还没有被市场广泛关注,在当前进行研究和布局非常有意义。

二、先进封装四大工艺

目前,带有倒装芯片(FC)结构的封装、晶圆级封装(WLP)、系统级封装(SiP)、2.5D封装、3D封装等均被认为属于先进封装范畴,这些先进封装大量使用RDL(再布线)、Bump(凸块)、TSV(硅通孔)、Wafer(晶圆)等基础工艺技术。RDL、TSV、Bump、Wafer也称为先进封装四要素。

1)Bump(凸块)技术,凸块是定向指生长于芯片表面,与芯片焊盘直接或间接相连的具有金属导电特性的突起物。普遍应用于Flip-Chip(倒装焊)技术中,处于晶圆之间互联的位置,起着电气互联和应力缓冲的作用,其发展趋势是使金属凸点越来越小,直至发展为HybridBonding(混合键合)技术,该技术制造的电介质表面光滑、没有凸点,且具有更高的集成密度;

2)RDL(重布线层)技术,用于X与Y平面电气延伸和互联。在晶圆表面沉积金属层和相应的介质层,并形成金属布线,对I/O端口进行重新布局,将其布局到新的,占位更为宽松的区域,并形成面阵列排布,RDL广泛应用于WLP(晶圆级封装)技术和2.5D/3D技术中,但不适用于Flip-Chip技术;

3)Wafer(晶圆)技术,可以用作芯片的基底和WLP封装的载体,也可以与硅基板一同实现2.5D集成,技术发展趋势是使Wafer面积逐渐增大;

4)TSV(硅通孔)技术,是一种利用垂直硅通孔实现芯片互连的方法,相比于传统引线连接,具有更短的连接距离、更高的机械强度、更薄的芯片厚度、更高的封装密度,同时还可以实现异种芯片的互连。

三、先进封装趋势下,传统封测环节的量价提升

在先进封装的产业趋势下,传统封装的半导体封装设备多数环节会有量价齐升的逻辑,市场空间会变得非常大。同时,先进封装里面其实是引入了包括像RDL、TSV等新工艺,带来新的设备增量需求。

然后再分别展开汇报一下这两个逻辑。

减薄环节。传统的半导体封装的流程中,第一道背面减薄,用的是化学机械抛光设备。在先进封装中,比如3D封装,需要把芯片叠好几层,为了让体积更加精致,需要把晶圆磨得更薄。因此减薄设备的需求量会增加。同时,为了把晶圆做薄,工艺对设备控制等各方面的要求更高,因此设备的价值量也会提高。

半导体划片环节。先进封装工艺的Chiplet,芯片的体积变小,芯片数量增多。对于半导体划片机来说,首先需要切更多的刀数,划片机的需求量肯定上升的。然后因为芯片变得更小,所以切割精度要求也变得更高。所以半导体划片机的价值量也提高,又是量价提升的逻辑,市场空间也会增大。代表公司:光力科技。

固晶环节。因为芯片数量变多,并且变得更小,工艺对固晶需求量增加,同时精度需求提高,也带来了价值量的提高,所以也是量价齐升的逻辑。代表公司:新益昌。

键合环节。半导体键合机,对于半导体键合机来说它的逻辑有点受损,先进封装倒装工艺主要是通过凸块进行连接的,不用导线。

塑封环节。在先进封装工艺中,结构更加复杂,塑封难度增加。,如果要保持原来的效率,塑封机的需求必须增加;塑封难度的增加,也带来了价值量的增加,市场规模大幅度增长。代表公司:文一科技。

测试、分选环节。典型的Chiplet是在一个大的芯片里面封装非常多的小芯片,在封装中,必须要保证这十多个小芯片比必须完好无缺。如果有一个芯片是坏的,整个大芯片都要一起报废。所以在先进封装里面对于测试的要求提高,而且一定是要上全检,所以也是量价齐升的逻辑。代表公司:精测/飞测(量测)、长川/华峰/精智达(测试) 。

四、封测产业新工艺催生新需求

凸块工艺。凸块工艺就是在晶圆上种植锡球,替代传统的引线键合工艺。凸块的一个工艺流程是涂胶显影曝光,如果是铜凸块就用电镀的设备,让铜柱子长出来;如果锡凸块就是在用晶圆植球设备把锡球植到晶圆上面,然后再用回流焊设备把锡球融化、再冷却。代表公司:芯源微、盛美上海。

曝光设备。国内的公司有两个,分别是上海微电子和芯碁微装。上海微电子是非直写光刻,芯碁微装是直写光刻。从精度上面看,上海微的产品应该有两款,分别是1微米和2微米,芯碁微装的产品是2微米。但是芯碁微装的直写光刻的优点就是灵活度更高。

电镀设备。国内现在还没有做的特别好的企业,还需要再跟踪。

植球设备。国内做的比较好的是凯格精机。这个公司以前是做PCB里面的锡膏印刷设备,现在拓展晶圆设备,产品已经做出来了,现在是在等客户和订单,也在紧密的跟踪。

回流焊设备。国内的公司就是尽拓股份,PCB回流焊设备龙头,现在拓展晶圆级回流焊设备,已经有产品了,在等客户和订订单的进展。

TS硅通孔工艺。2.5D或者3D封装涉及到硅通孔工艺。比如说像3D封装增加了一个Z轴,芯片叠芯片,必须在下层的芯片上面打孔,在孔里面做铜或者银之类导电的金属支柱,让最上层的芯片和最下边的闸板连接到一起。

然后硅通孔的工艺首先是用蚀刻设备在晶圆上面去做凹槽,做完凹槽之后用薄膜沉积设备在上面做上绝缘层阻挡层。然后还有种子层,再往后面就是用电镀设备把铜的柱子给电镀出来。再往下面就是需要用背面减薄设备,是把凹槽下面那部分不导通的部分剪薄掉,这样就会形成一个贯穿孔。

硅通孔工艺流程涉及到的设备大部分是前道设备,包括刻蚀设备、薄膜沉积设备、化学机械抛光设备。

再布线工艺。2.5D和3D封装中,在芯片和基板之间再加了一个中间层,承上启下,一边和上面的芯片连接,一边和最下面的基板连接。中间层有比较多的线路,所以叫再布线工艺。

再布线工艺像线路板的制作的过程,比较核心的设备主要是曝光设备。

五、塑封设备行业的量价齐升的逻辑

塑封设备是在用凸块把芯片和夹板或者芯片和框架连接后,用环氧塑封料包裹起来形成比较稳定的芯片结构。

传统半导体塑封设备的市场空间是在30-40亿人民币左右,然后在先进封装的影响下,塑封设备市场空间大幅度增长,预计将达到百亿量级。

塑封设备市场空间增长的原因:

首先,先进封装的塑封效率会比传统封装低得多。像传统的塑封机,做两片大概是需要三十五秒钟,而先进封装里面晶圆级封装的塑封设备封装一片晶圆需要十五分钟。要保持原来的效率,就需要更多的设备。

同时,设备难度的增加会带来塑封设备价值量的提升。传统的塑封设备,一拖四180吨的价值量大约在450万人民币,而晶圆级封装的塑封设备价值在一千多万到两千万水平。

竞争格局,传统的半导体数控设备国产化率很低,在30-40亿的市场规模,国产化率不到10%。加上塑封设备非标定制化较多,导致上游设备企业体量很小,竞争力弱。

先进封装数控设备现在市场上最新的进展是文一科技率先取得了技术突破,并且取得了客户签单进展。国产设备能够快速突破的原因,半导体塑封设备是有比较高的定制化因素在里面的,需要对客户的工艺制程有比较深入的一些了解,而国内的企业还是占着主场优势;同时,上下游的企业也有比较强的设备国产化需求。

特别提醒:本文为投资逻辑分享,不构成投资建议。

下载APP

下载APP

下载APP

下载APP